A new version of this project is available here

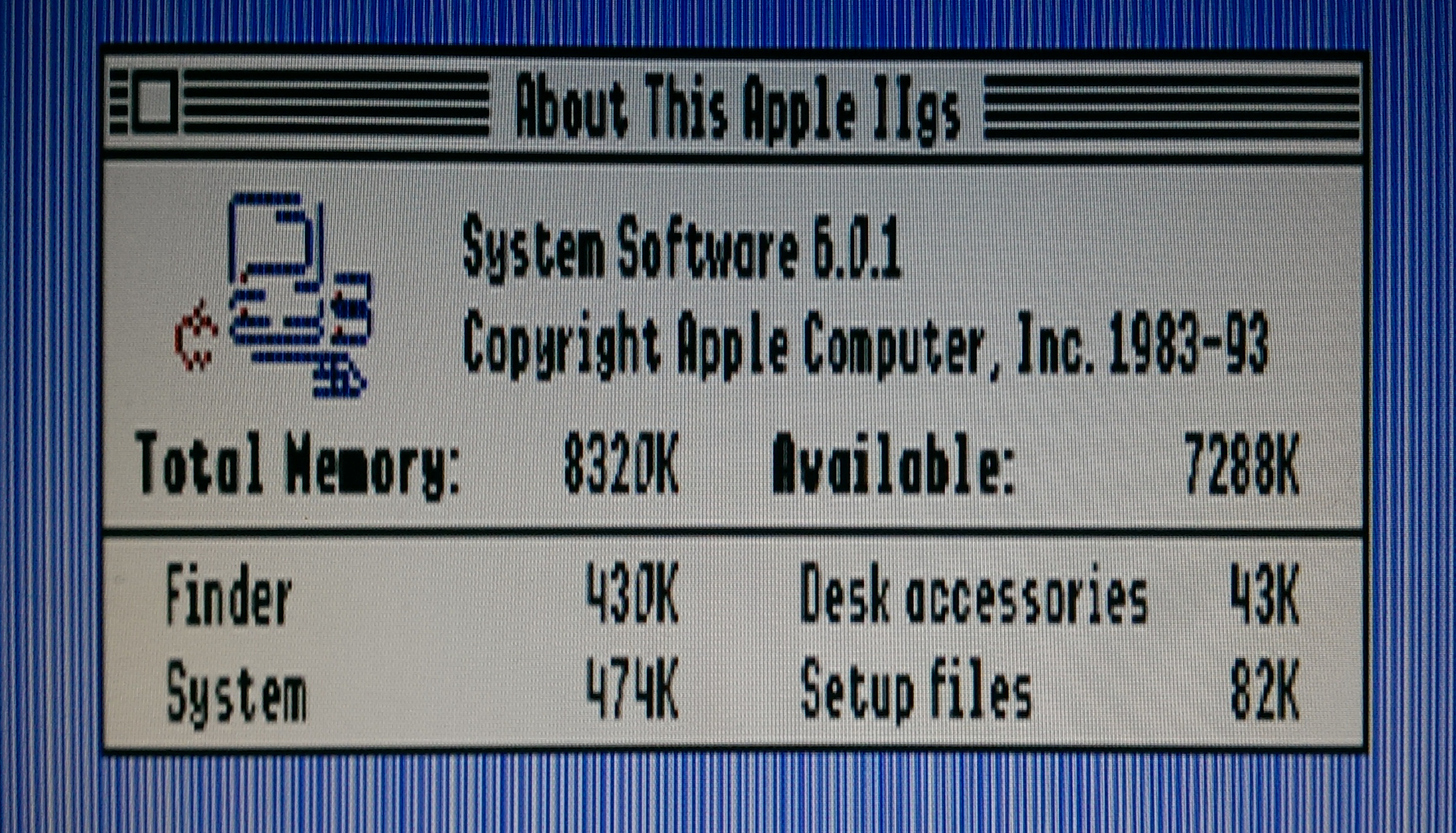

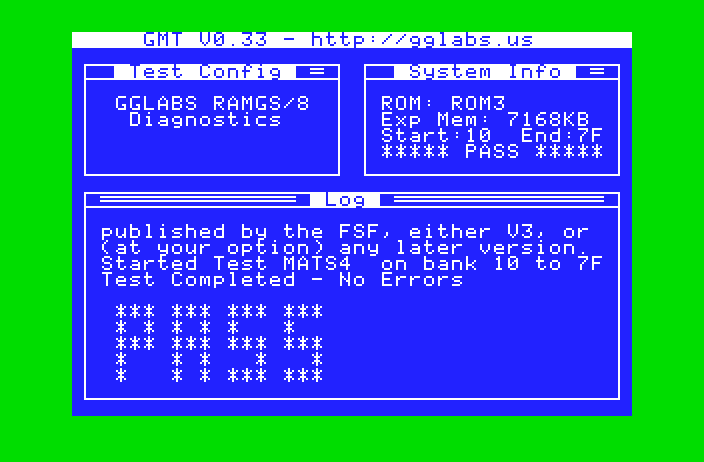

The apple IIgs is the most advanced computer in the Apple II series. Equipped with a 65c816 8/16-bit CPU with 24-bit address space it could address up to 16MB of memory. The original rom 01 model shipped with 256KB of fast RAM, the revised rom 3 shipped with 1MB (both had an additional 128KB of standard RAM and 64KB of sound RAM). RAMGS is a newly designed 8MB expansion card for this great classic computer.

The apple IIgs is the most advanced computer in the Apple II series. Equipped with a 65c816 8/16-bit CPU with 24-bit address space it could address up to 16MB of memory. The original rom 01 model shipped with 256KB of fast RAM, the revised rom 3 shipped with 1MB (both had an additional 128KB of standard RAM and 64KB of sound RAM). RAMGS is a newly designed 8MB expansion card for this great classic computer.

This design builds on what we learned building the older RAMGS/8 and RAMGS/4. We combined the use of a simple PLD to generate the control signals and a single 8Mx8 DRAM. This allowed us to reduce the PCB size to 58x40mm.

The address bus FRA0-FRA9 is connected though series termination directly to the corresponding DRAM pins (note the signal swaps to simplify the routing). The PLD implements 2 main functions: generates a modified WE# for the DRAM (see section at the end of the article for a detailed explanation) and multiplexes CROW0, CROW1 and a latched version of D6 (which represents A22) into the correct DRAM address signals.

The address bus FRA0-FRA9 is connected though series termination directly to the corresponding DRAM pins (note the signal swaps to simplify the routing). The PLD implements 2 main functions: generates a modified WE# for the DRAM (see section at the end of the article for a detailed explanation) and multiplexes CROW0, CROW1 and a latched version of D6 (which represents A22) into the correct DRAM address signals.

The card can be configured for 4 or 8MB. To limit the memory to 4MB is necessary to add R16 and cut the short under jumper J1.

Address Drive Strength

Most vintage expansion cards buffer the address to the drams on the card. After extensive probing on our previous cards it turns out that the buffers are unnecessary on the ramgs because of the limited loading (2-9 loads depending on the SIMM type and size) and short traces (about 80mm). For comparisons the apple 1MB expansion card has 32 loads and traces exceeding 300mm. Actually the FPI I/O drive is already too strong for the ramgs layout given the negative overshoot exceeds 2V in the scope captures.

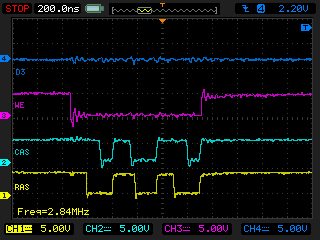

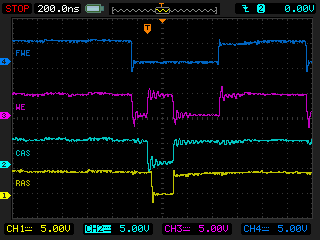

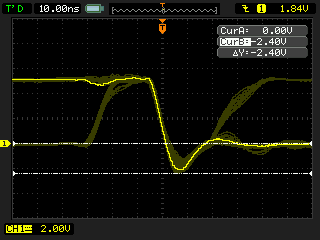

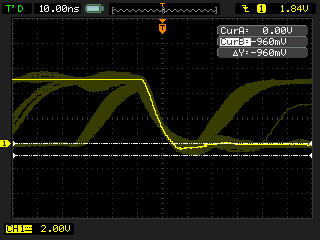

Adding series termination on the address lines reduces the overshoot at the expense of slower rise and fall time. The following two images show the effect of 56ohm and 100ohm series termination.

4Mbit Support

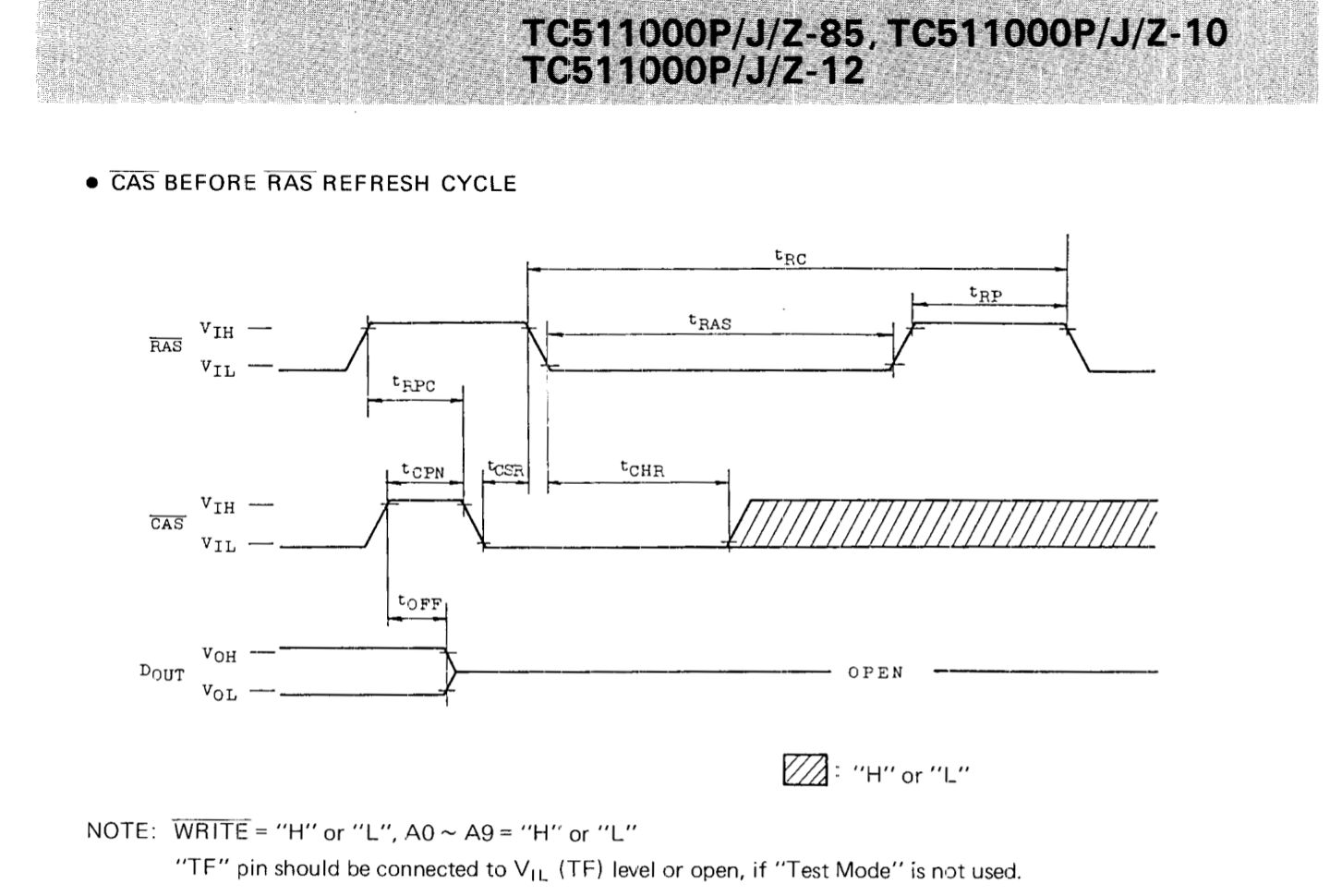

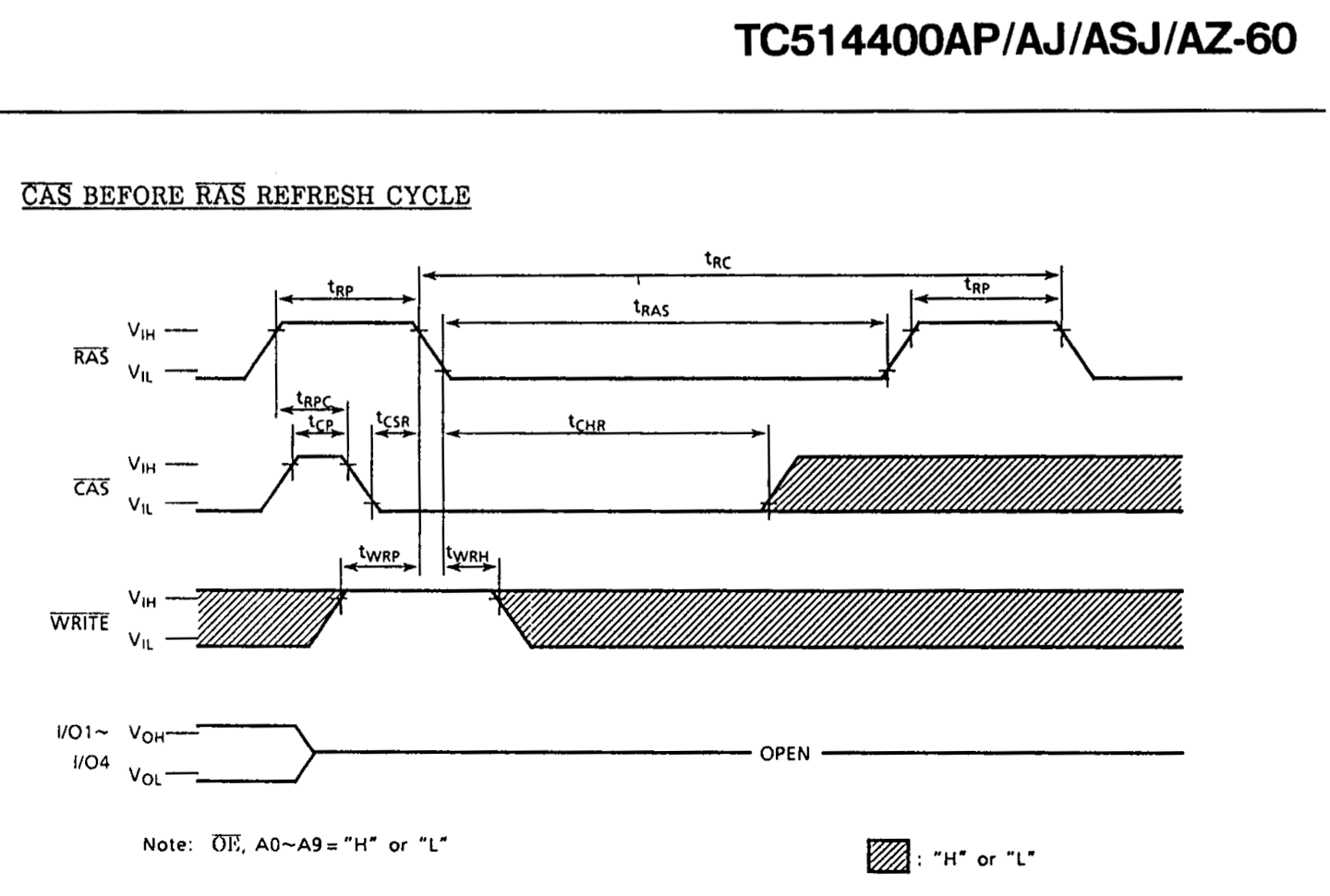

The Apple IIgs seems to perform only standard read cycles, early write cycles and CAS before RAS refresh cycles. We have not seen any fast page mode nor read-modify-write cycles.

Upon close inspection of the memory datasheets is clear that the CAS before RAS refresh cycle is different between the 1Mbit and the 4Mbit (or larger) parts. In particular, the larger devices require WE to be high at the falling edge of RAS (WE is a don't care in the 1Mbit devices). Issuing a RAS before CAS refresh cycle with WE low on the 4Mbit DRAM enables the device test mode.

The IIgs follows the 1Mbit specification and the state of WE during a refresh cycle is undetermined (it is actually the state left by the transaction right before the refresh cycle). This behavior randomly enables the test mode in the memories with catastrophic results to the running programs.

The two scope shots below show the apple IIgs behavior on the left (WE# stays low during a refresh cycle), and the output of the PLD (WE# is deasserted during a refresh cycle).