A new version of this project is available here

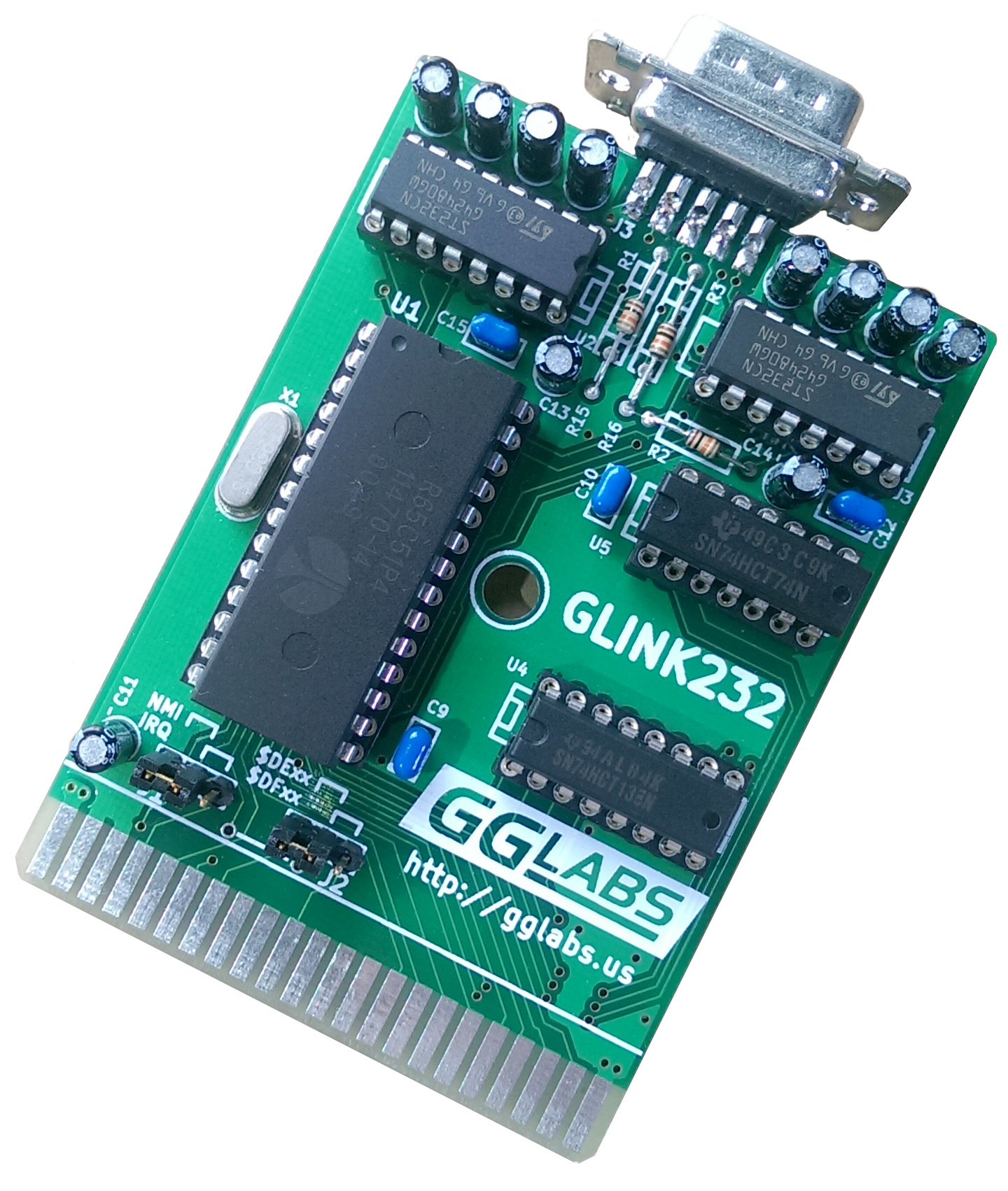

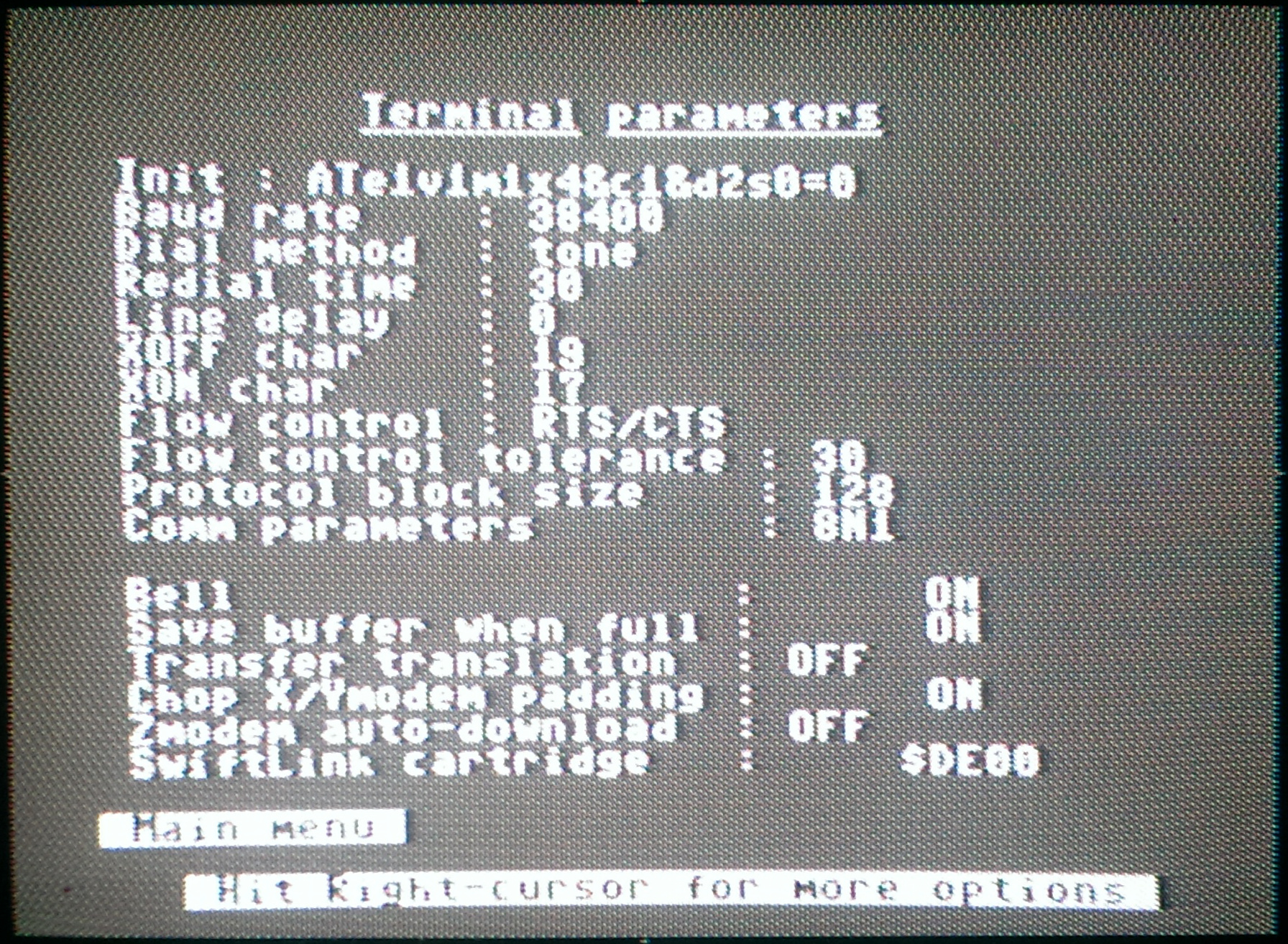

Both the commodore 64 and the 128 have a software UART implementation that limits the useful speed to 2400 bauds. To work around this limitation Dr. Evil Labs and later CMD produced the SwiftLink232 and Turbo232 cartridges based on the 6551 ACIA chip. Both of these have been out of production for a very long time. GLINK232 is a modern replacement for the swiftlink232 allowing the commodore 64/128 to communicate at speeds up to 38400 bauds.

Both the commodore 64 and the 128 have a software UART implementation that limits the useful speed to 2400 bauds. To work around this limitation Dr. Evil Labs and later CMD produced the SwiftLink232 and Turbo232 cartridges based on the 6551 ACIA chip. Both of these have been out of production for a very long time. GLINK232 is a modern replacement for the swiftlink232 allowing the commodore 64/128 to communicate at speeds up to 38400 bauds.

Similarly to the SwiftLink, the card can be configured using jumpers at either the $DE00 or $DF00 I/O address and can use either the NMI or IRQ interrupt line (most native software use NMI, but CP/M uses IRQ).

The card uses a 3.6864MHz crystal (double the standard for a 6551) to match the baud rate table of the SwifLink.

The A02 version of the GLINK232 adds a timing fix to support the CMOS version of the 6551. This fix will allow the use of more modern 6551 implementation including the Western Design Center W65C51 which is the only 65xx series ACIA still in production.

The board has multiple configuration options:

- Modem control - adds DTR, DCD and DSR, minimal configuration supports RX/TX and CTS/RTS only

- Jim Brain's HS232 I/O decoder - reduces I/O aliasing to support multiple cards

- Support for 65C51 ACIA - Adds support for the lower power CMOS version of the 6551

BOM Options

| Modem Control | CTS/RTS only | Full Modem Control |

|---|---|---|

| C5 | no stuff | 1uF |

| C6 | no stuff | 1uF |

| C7 | no stuff | 1uF |

| C8 | no stuff | 1uF |

| C14 | no stuff | 10uF |

| U3 | no stuff | MAX232 |

| I/O Decoder | SwifLink | HS232 |

| J4 | wire | no stuff |

| R4-R11 | no stuff | 0 ohm (one location only) |

| U4 | no stuff | 74HCT138 |

| ACIA Support | NMOS only | CMOS and NMOS |

| R14 | 0 ohm | no stuff |

| C10 | no stuff | .1uF |

| U5 | no stuff | 74HCT74 |

CMOS Support

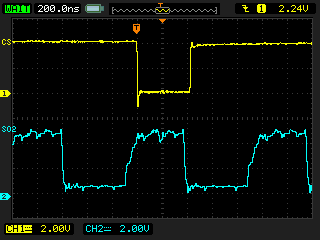

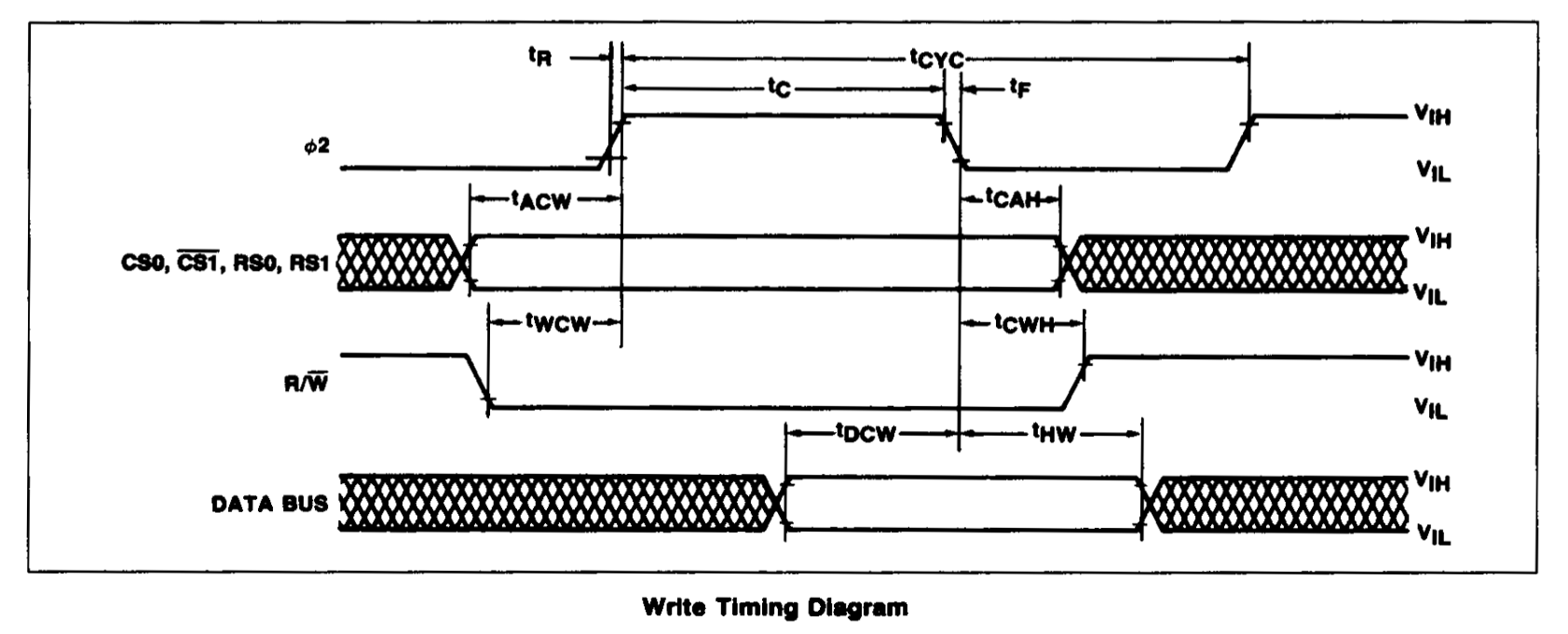

The signals at the Commodore 64 cartridge port do not meet the timings of standard 65xx peripherals. Specifically the tACR/tACW (address setup time vs phi2 clock) parameter is violated as the rising edge of phi2 is before the falling edge of I/O1 or I/O2.

It turns out that most NMOS 65xx devices are tolerant of this violation. This is the reason why Jim Brian's HS232 and other Swiftlink clones that omit the 7474 flip flop work despite the timing issue.

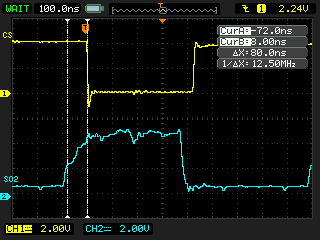

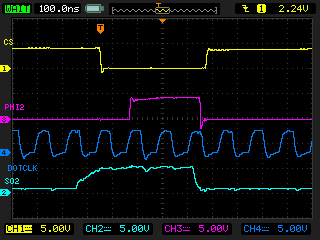

The CMOS version of the 6551 is not tolerant of the timing violation and fail to operate correctly without a timing fix. The circuit uses a 7474 dual flip flop clocked by the 14MHz dot clock. This has the effect of delaying the rising edge of phi2 by at least one full 14MHz period to allow enough setup time for the CS signal. The phi2 clock is also connected to the flip flop asynchronous reset to keep the falling edge aligned with the phi2 clock from the C64.

The timing fix will reduce the high time of the phi2 clock going into the 6551. To meet the tC (phi2 pulse width) of the ACIA a 2MHz or faster version is required.