A new version of this project is available here

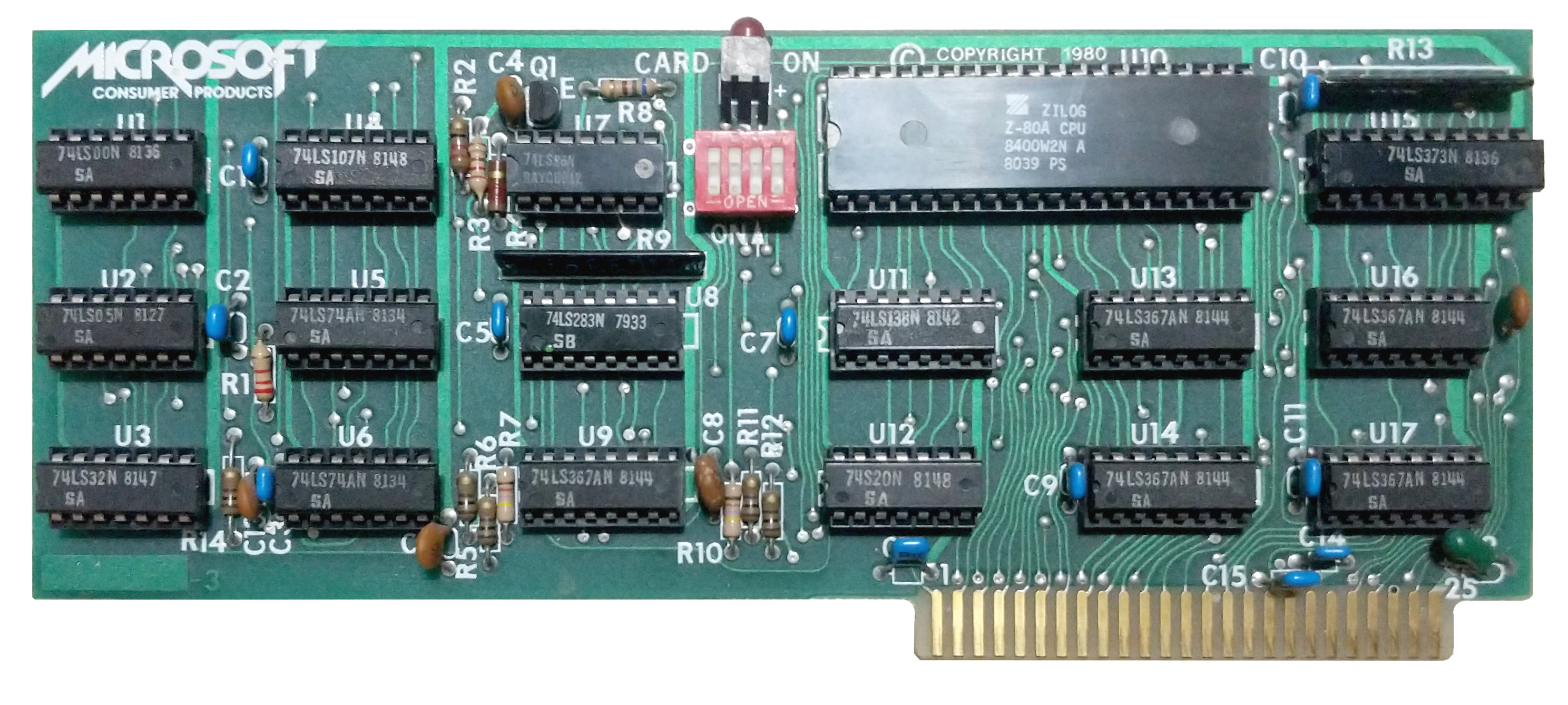

The Microsoft Softcard was the first card to allow CP/M software to run on the Apple II. It was originally developed to simplify the porting of Microsoft Basic to the Apple II. It turned out to be a great success and at some point in time it was the most popular CP/M platform in use.

The Microsoft Softcard was the first card to allow CP/M software to run on the Apple II. It was originally developed to simplify the porting of Microsoft Basic to the Apple II. It turned out to be a great success and at some point in time it was the most popular CP/M platform in use.

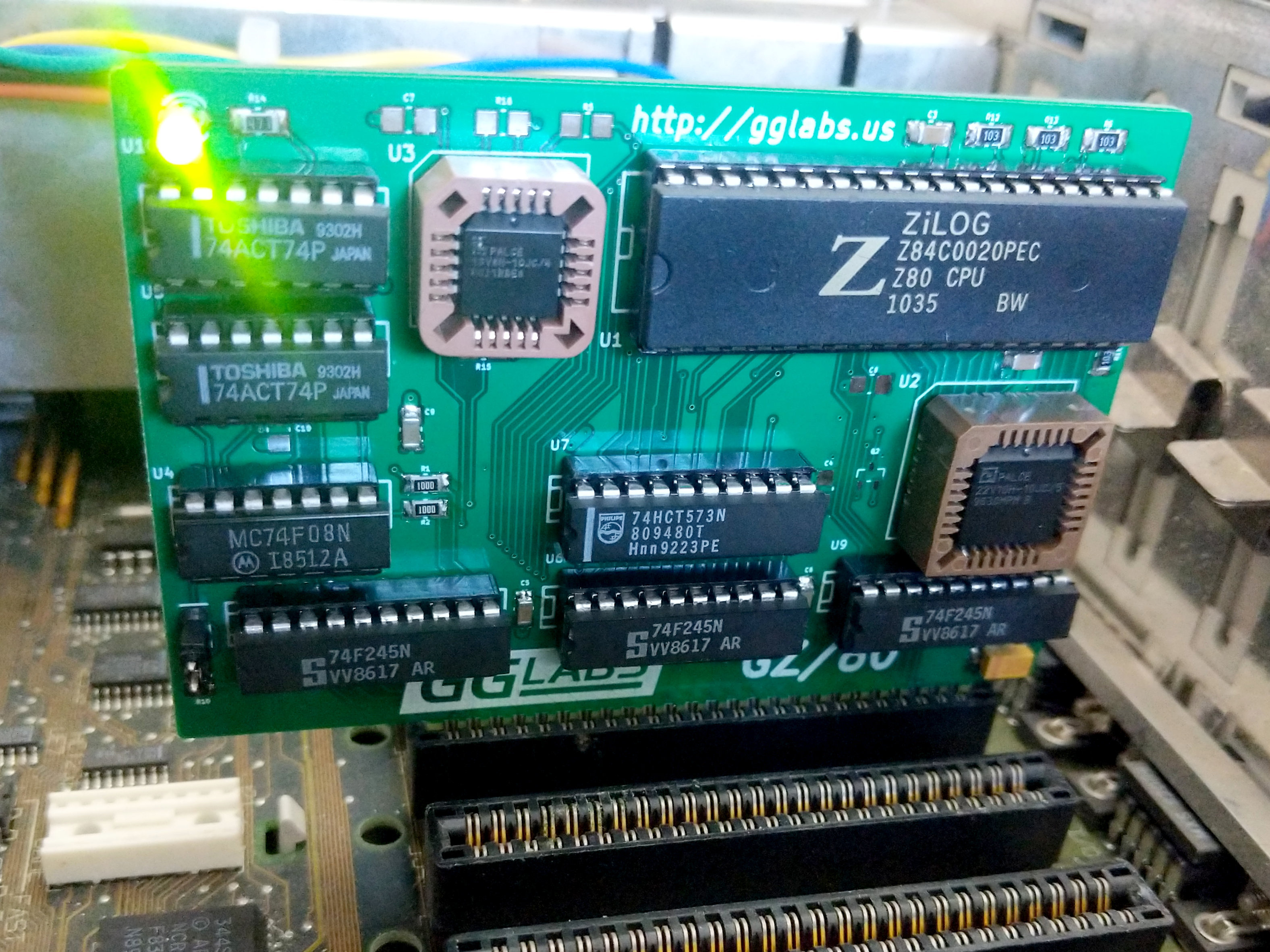

This success prompted the development of many compatible cards. Some exact copies, some enhanced or cost reduced. The GZ/80 is a modern implementation of a Softcard compatible card with an additional turbo mode with approximately double the speed of the original card.

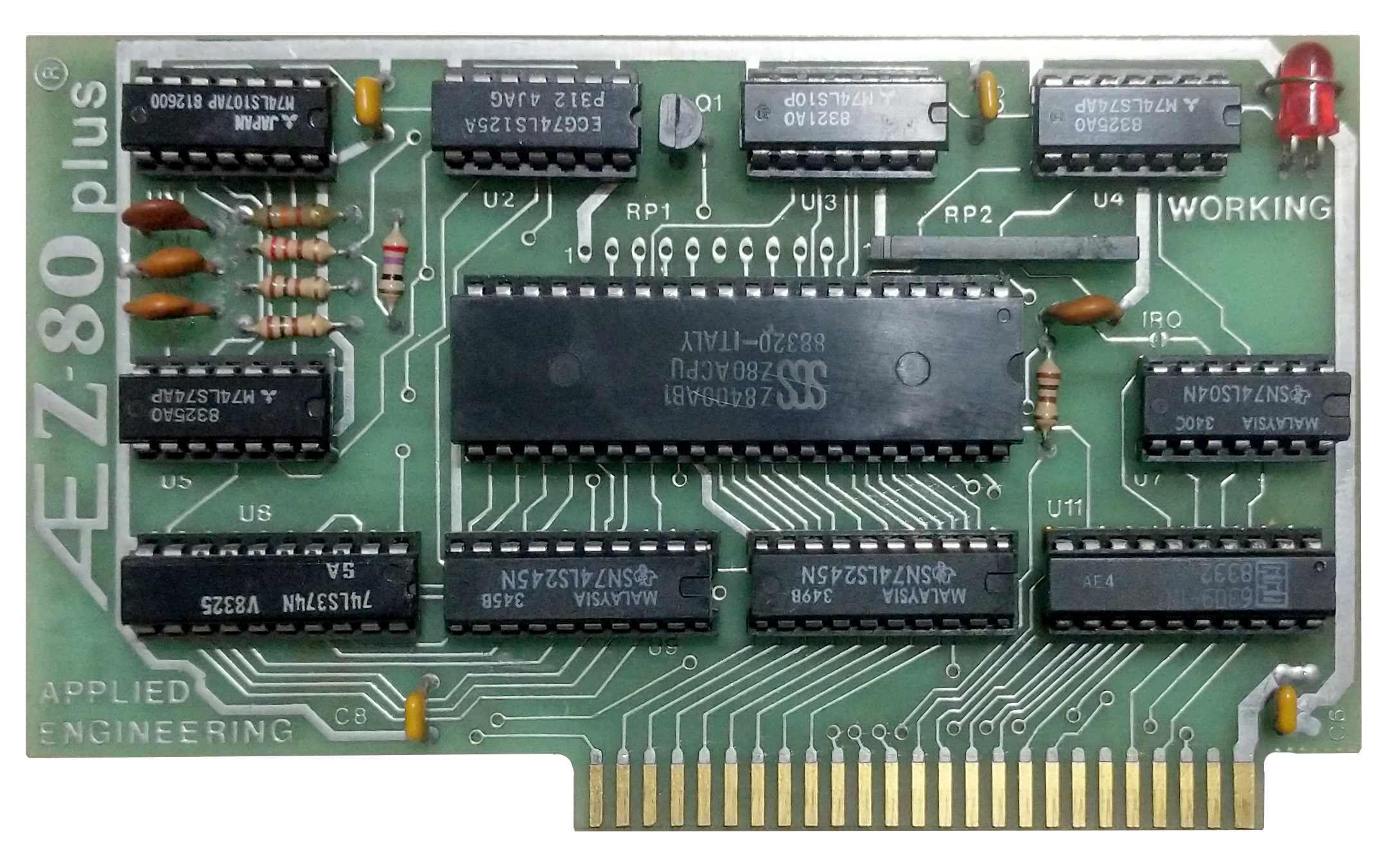

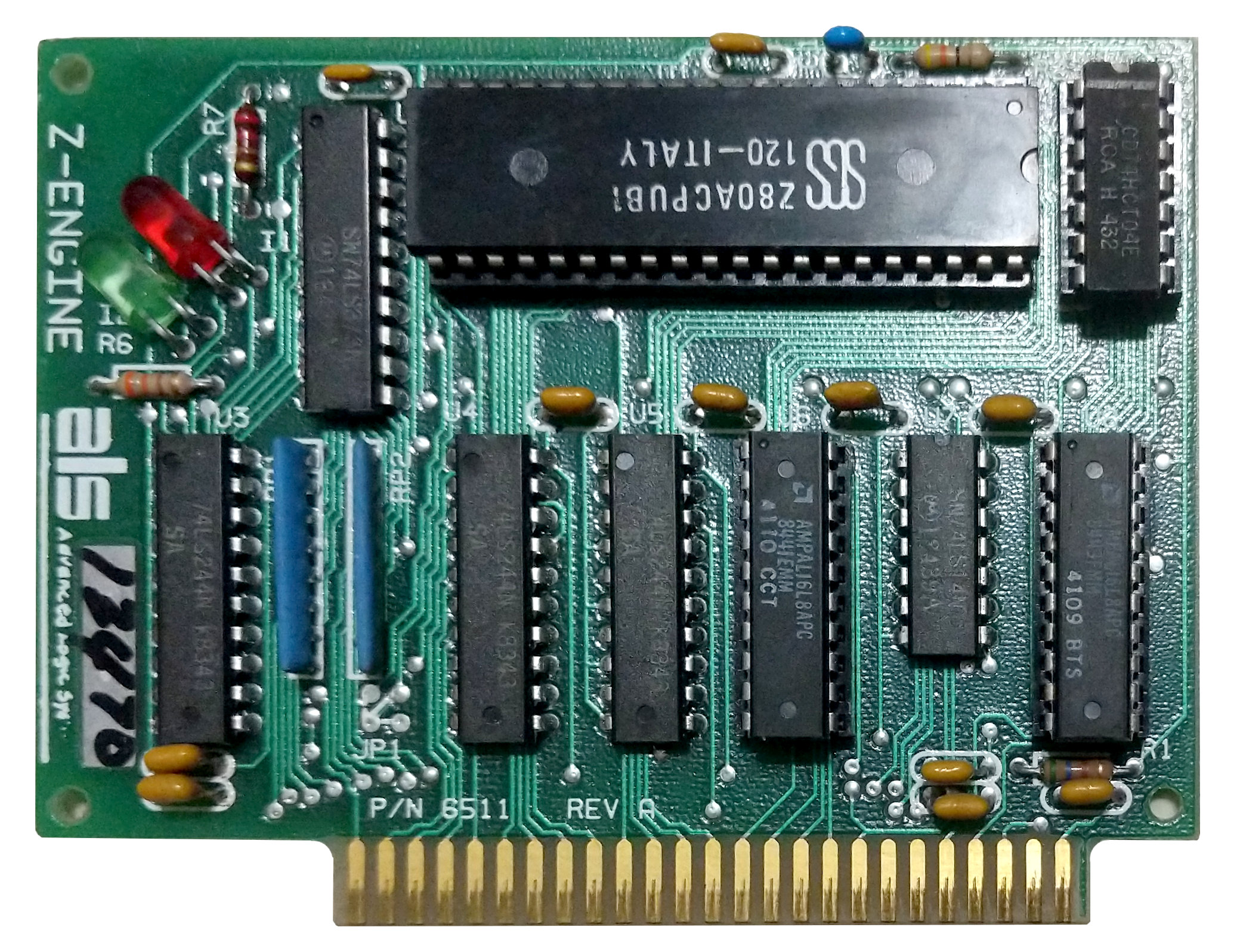

During the development of the card we studied the original Microsoft schematics, the Applied engineering AZ-80 plus and the ALS Z-Engine. The GZ/80 implements the same subset of functionality implemented in the AE AZ-80 and the ALS Z-Engine.

This is equivalent to the original Microsoft Softcard with all the dip switches in the default configuration (Address translation enabled, no Z-80 interrupts, no DMA). There is virtually no loss in actual functionality as none of these features were ever implemented in any of the Apple II CP/M versions.

The Microsoft Softcard is designed completely using standard TTL logic chips. This made it very easy to reverse engineer and fully understand the circuit. Schematics were also provided in the SoftCard manual. The AE Z-80 plus removes most of the unused features (ability to disable address translation and DMA support). Z-80 interrupts are supported by adding a solder bridge. This simplification and the implementation of address translation using a 256 bytes PROM instead of discrete logic reduced the total chip count from 17 to 11.

The Z-Engine further refines the design by using 2 PALs to bring down the total chip count to 9.

GZ/80 Schematics

In all SoftCard compatible cards the Z-80 uses the Apple II main memory for all processing.  The Z-80 clock runs only during PH1 so no Z-80 wait states are required. The GZ/80 follows the same in "normal" mode. In turbo mode the Z-80 clock runs constantly and the Z-80 WAIT# signal is used to synchronize the Z-80 memory accesses to the Apple II bus.

The Z-80 clock runs only during PH1 so no Z-80 wait states are required. The GZ/80 follows the same in "normal" mode. In turbo mode the Z-80 clock runs constantly and the Z-80 WAIT# signal is used to synchronize the Z-80 memory accesses to the Apple II bus.

The GZ/80-A03 schematics is the same are the previous GZ/80-A02 with the addition of a small RC delay on PH0, PH1 and 7MHz clocks to improve the compatibility with some systems.

U5A, U5B, U4A, U4C and U4D take care of the Z-80 clock generation. U7 latches the data from the apple bus to the Z80.

The Z-80 is connected to the Apple II address and data bus using 3 octal tri state buffers (U6, U8, U9). The 74LS245 bi-directonal buffer was used because the pinout is a better match for the design vs. the uni-directional 74LS244. The gate U4B buffer the clocks for distribution on the card. The dual D-FlipFlop U13 is used to turn the card on and off. The GAL U2 perform the address translation and generates the remaining control signals. The GAL U3 contains the logic to generate the Z-80 WAIT# signal in turbo mode.

Card Testing

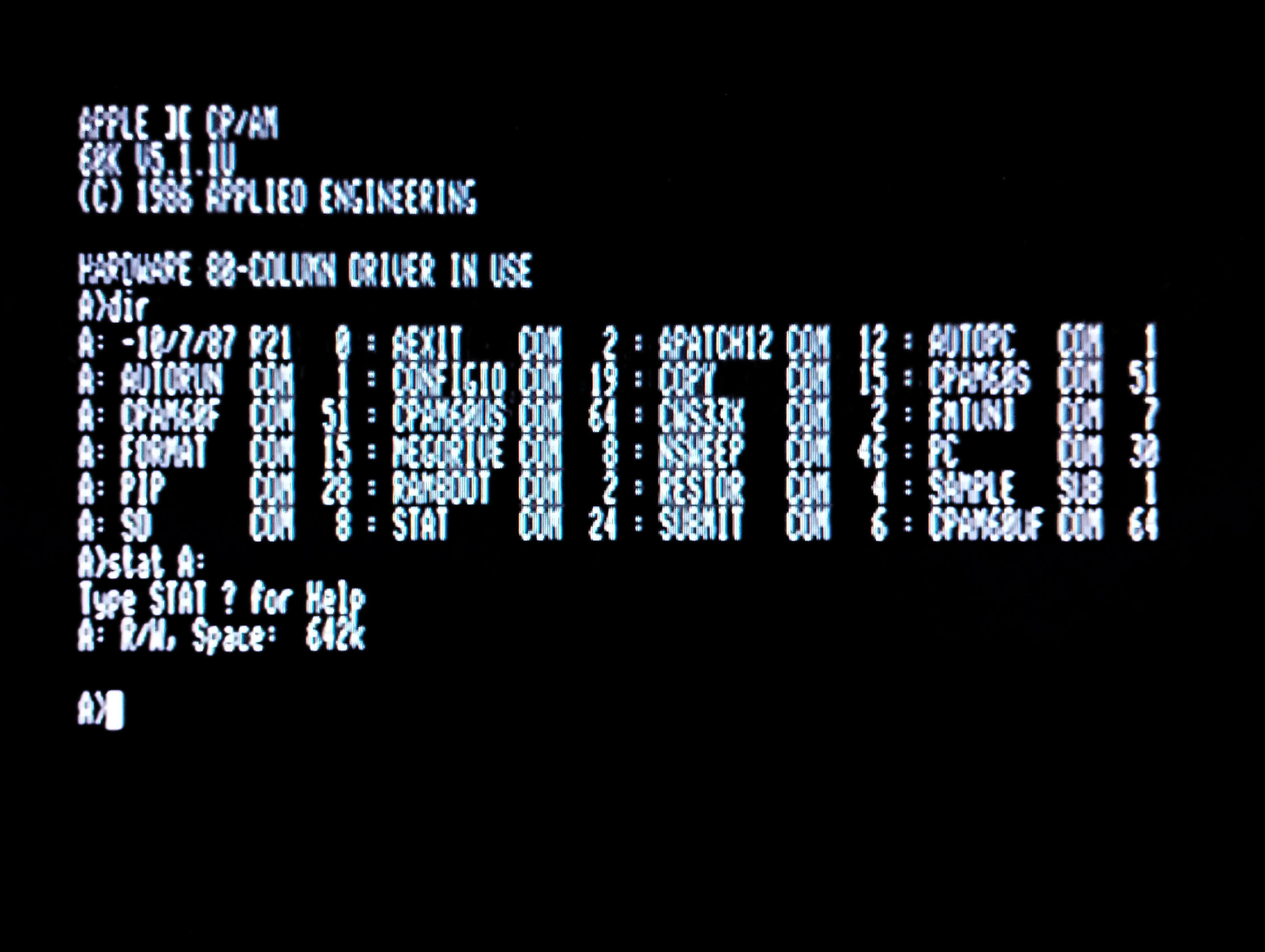

We tested the GZ/80 using many versions of CP/M and all worked as expected. On the IIgs it is necessary to set the slot where the card is placed to "own card". With the newer A01 and A02 cards it is no longer required to put the system in "slow" mode.

Our team particularly liked the AE CP/AM 5.1.1 as on a IIgs it allows to boot and operate exclusively on 3 1/2" floppies. CP/AM also seems to support smartport based hard drives, but we did not have enough time to test this functionality.

| CP/M Version | Test Result | Comments |

|---|---|---|

| Microsoft CP/M 2.20B | OK | |

| Microsoft CP/M 2.23 | OK | |

| AE CP/AM 4.0 | OK | |

| AE CP/AM 5.1 | OK | Could not get 3 1/2" to work |

| AE CP/AM 5.1.1 | OK | 3 1/2" works |

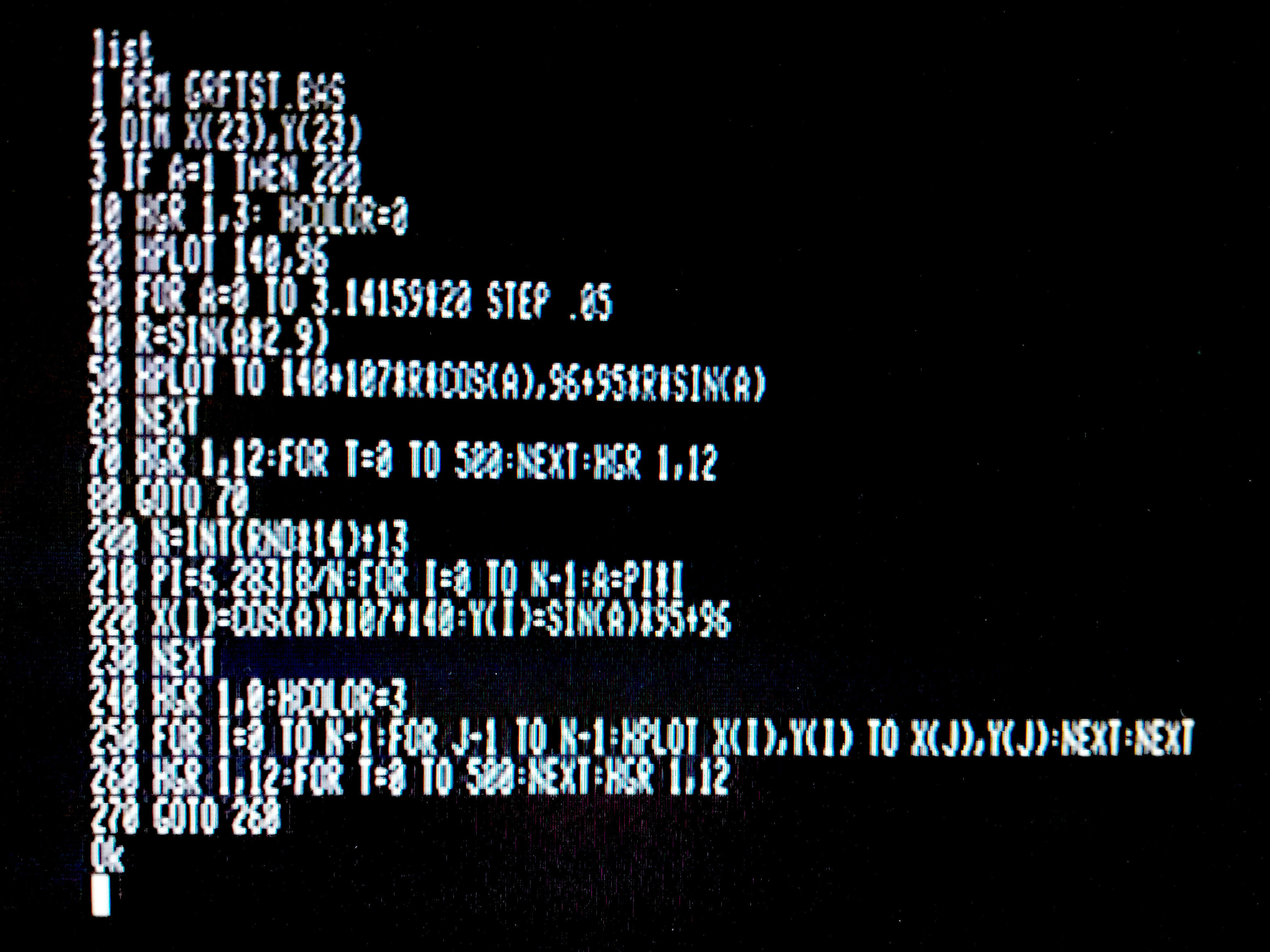

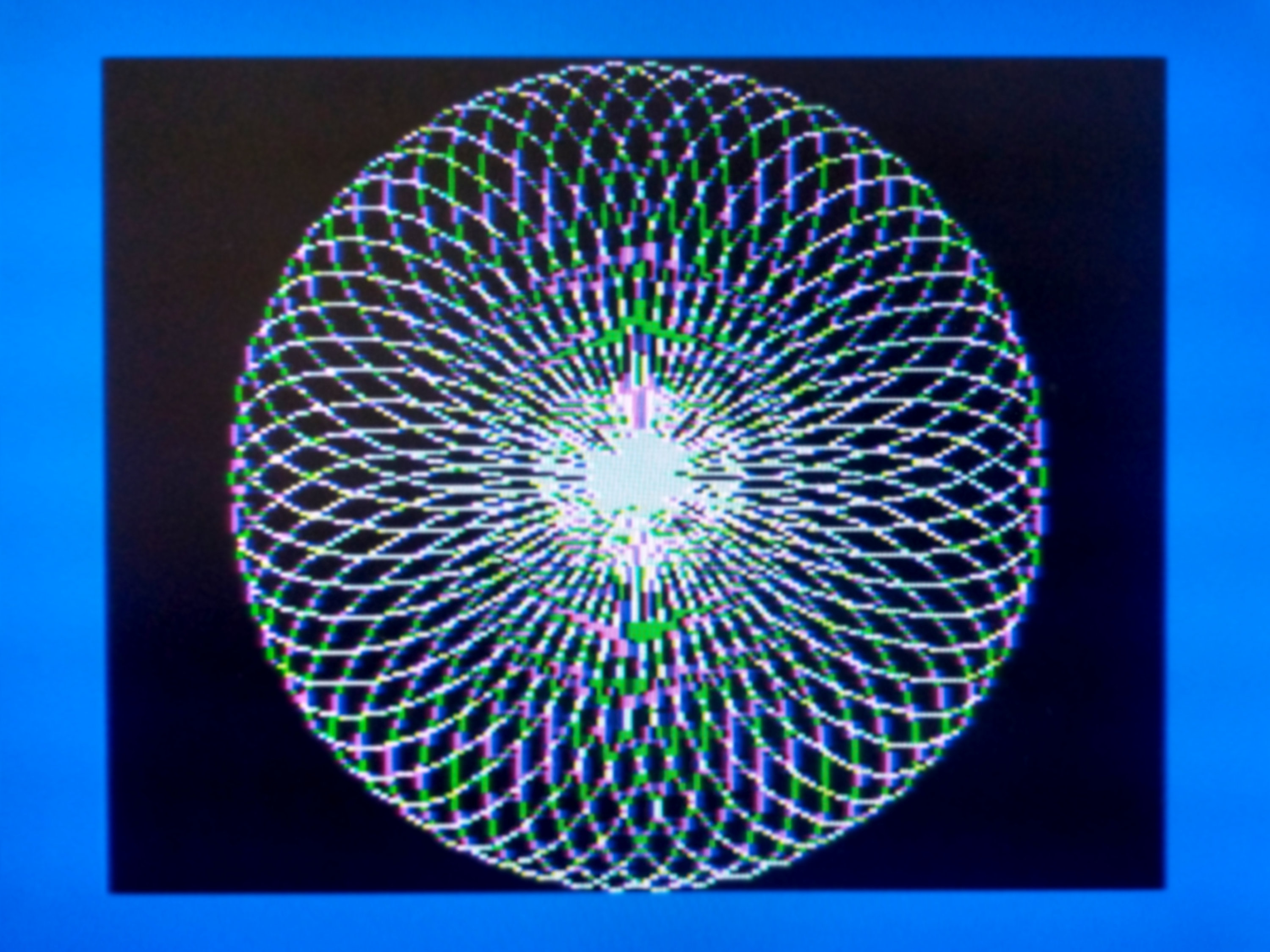

Turbo Mode

Analyzing the bus timing of the Z-80 and the Apple II it becomes evident that the Z-80 could run faster than the 2MHz of the original SoftCard. The GAL U3 takes care of generating the additional control signals to support faster Z-80 speeds. For the faster clock the obvious choice was to use the 7MHz clock already present on the apple II bus. Because the memory access are limited to 1MHz the effective speed is usually around 4MHz (which is slightly less than double the SoftCard).

In addition the higher Z-80 speed does not allow enough time for 6502 refresh cycles preventing the card from working on Apple systems equipped with the NMOS 6502. Only systems with a CMOS 65C02 or a 65C816 work properly in this configuration.

Turbo Mode is enabled by jumper J1.

| JP1 | Mode | HGR.BAS execution time (mm:ss) |

|---|---|---|

| 2-3 | 2MHz (original softcard timing) | 1:59 |

| off | 2MHz (enhanced timing compatible with IIgs fast mode) | 1:59 |

| 1-2 | 7MHz (turbo mode) | 1:06 |