A new version of this project is available here

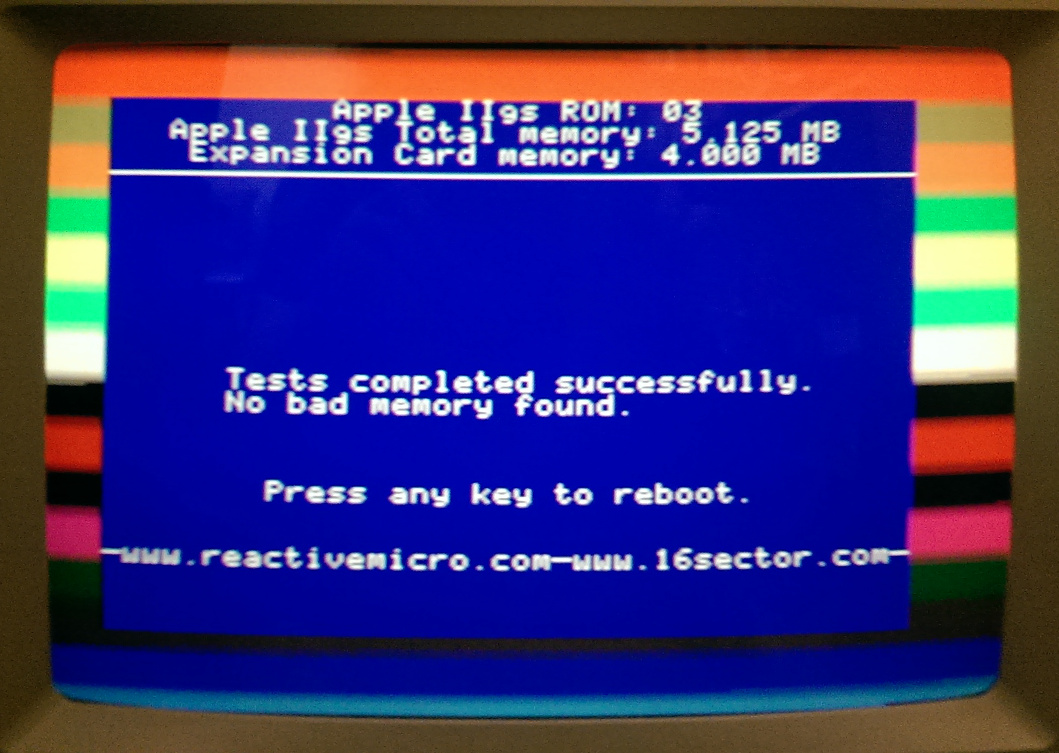

The apple IIgs is the most advanced computer in the Apple II series. Equipped with a 65c816 8/16-bit CPU with 24-bit address space it could address up to 16MB of memory. The original rom 01 model shipped with 256KB of fast RAM, the revised rom 3 shipped with 1MB (both had an additional 128KB of standard RAM and 64KB of sound RAM). RAMGS is a newly designed 4MB expansion card for this great classic computer.

The apple IIgs is the most advanced computer in the Apple II series. Equipped with a 65c816 8/16-bit CPU with 24-bit address space it could address up to 16MB of memory. The original rom 01 model shipped with 256KB of fast RAM, the revised rom 3 shipped with 1MB (both had an additional 128KB of standard RAM and 64KB of sound RAM). RAMGS is a newly designed 4MB expansion card for this great classic computer.

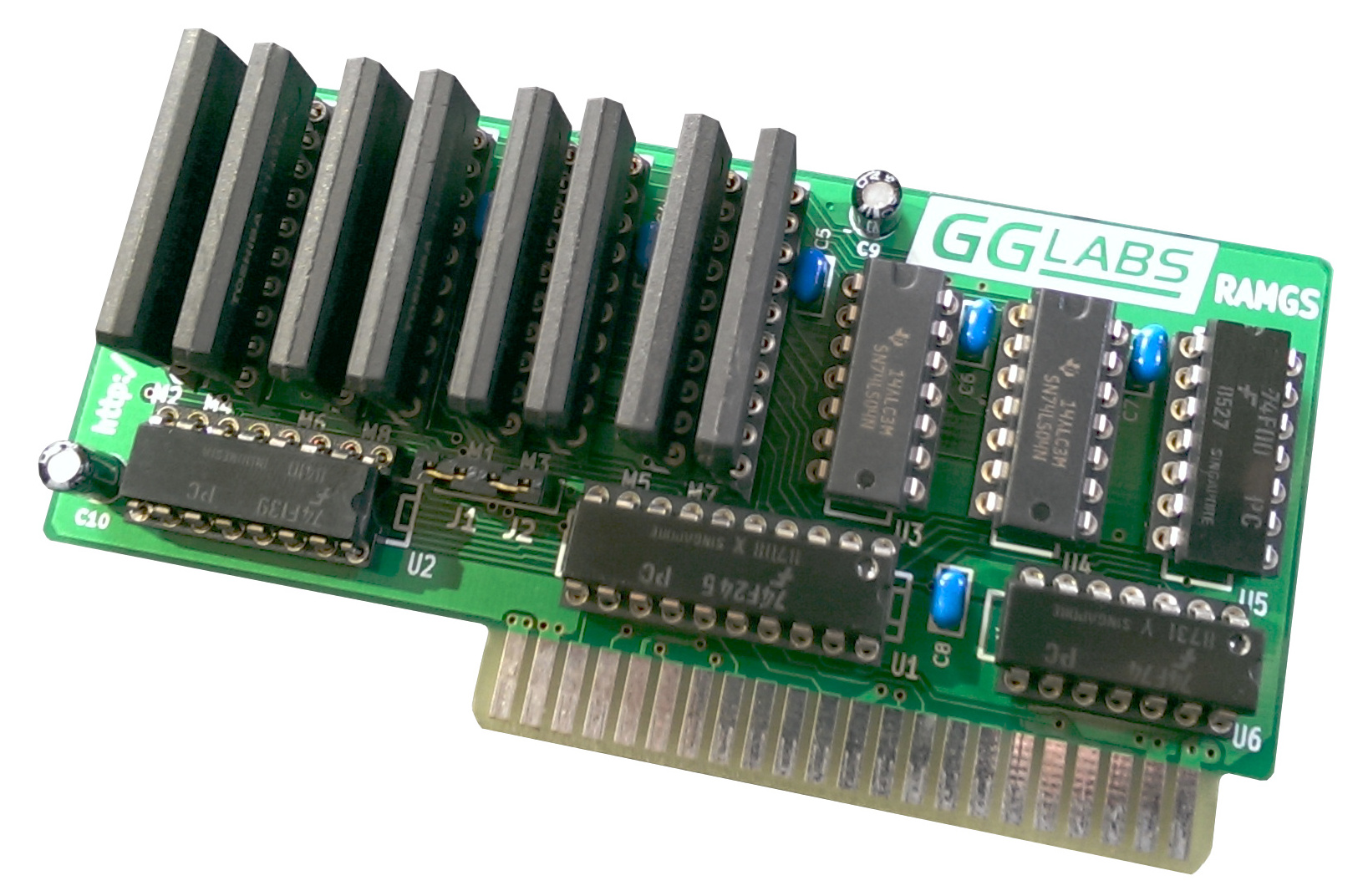

The design team goal was to build a small card to keep cost down but still try to keep a vintage look to the design. We ended up with a full PTH design using 4Mbit fast page DRAMs in a ZIP package. The schematics is very similar to the original Apple memory expansion card and many other clones of the time.

U1 is a bi-directional buffer for the data bus. A low on the CSEL signal is required to read the DRAM data.

U3 and U4 buffer the address bus. U2 decodes the RAM bank from the CROW0 and CROW1 signals.

The only modern twist is the addition of the U5-U6 circuit to add support for the 4Mbit DRAMs (see section at the end of the article for a detailed explanation).

The card can be configured for 1, 2 or 4MB (the 3MB configuration is not supported as recommended in the Apple documentation).

| Configuration | J1 | J2 | Memories |

|---|---|---|---|

| 1MB | off | off | M1, M2 |

| 2MB | on | off | M1, M2, M3, M4 |

| 4MB | on | on | M1-M8 |

The card accepts most fast page mode 1Mx4 DRAMs in the ZIP-20 package. Refer to the table below for part numbers.

| Manufacturer | Part Number |

|---|---|

| Siemens | HYB514400 |

| Toshiba | TC514400 |

| Hitachi | HM514400 |

| NEC | uPD424400 |

| Mitsubishi | M5M541000 |

| Oki | MSM514400 |

| Fujitsu | MB814400 |

| Samsung | KM44C1000 |

| Micron | MT4C4001 |

| TI | TMS44400 |

4Mbit Support

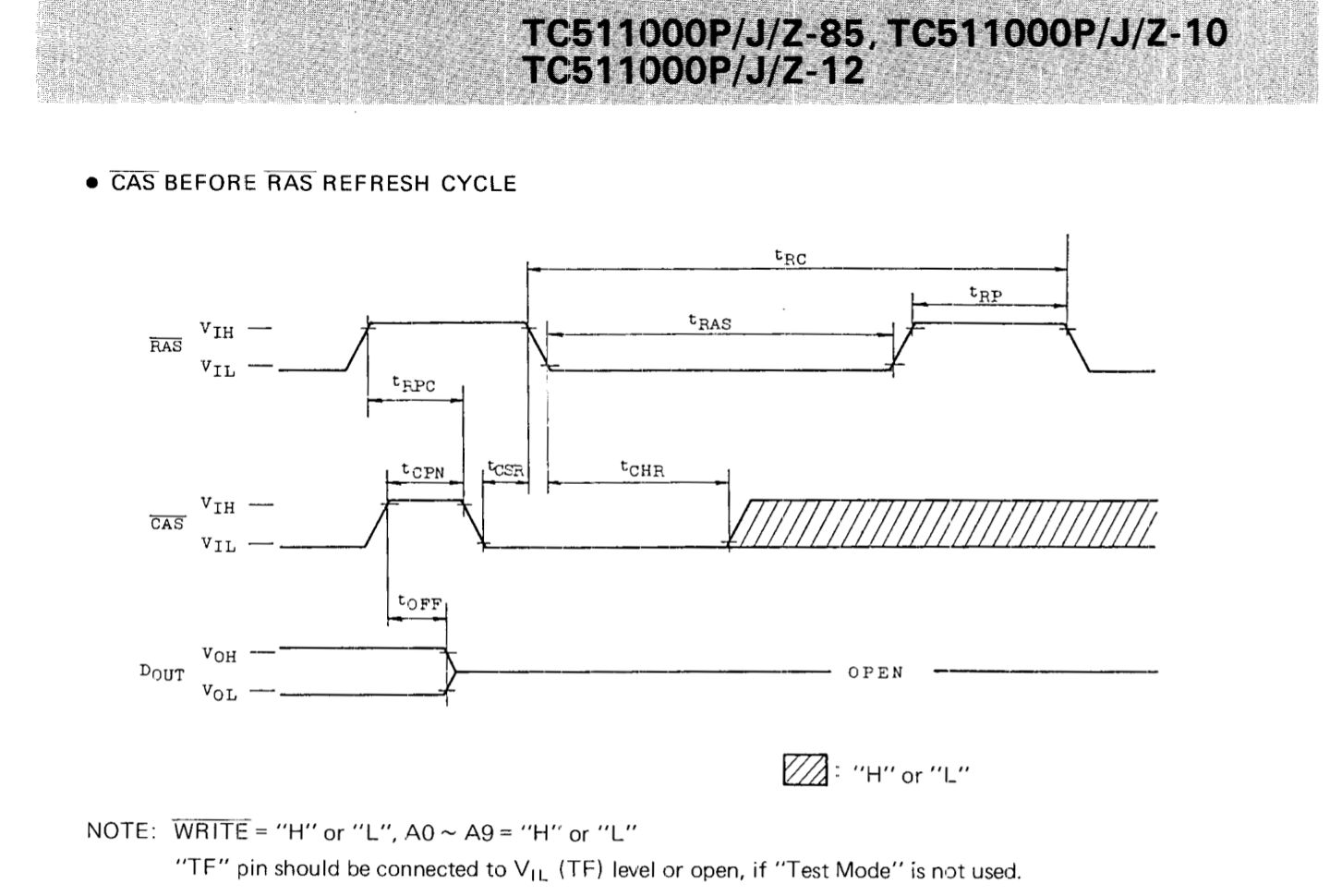

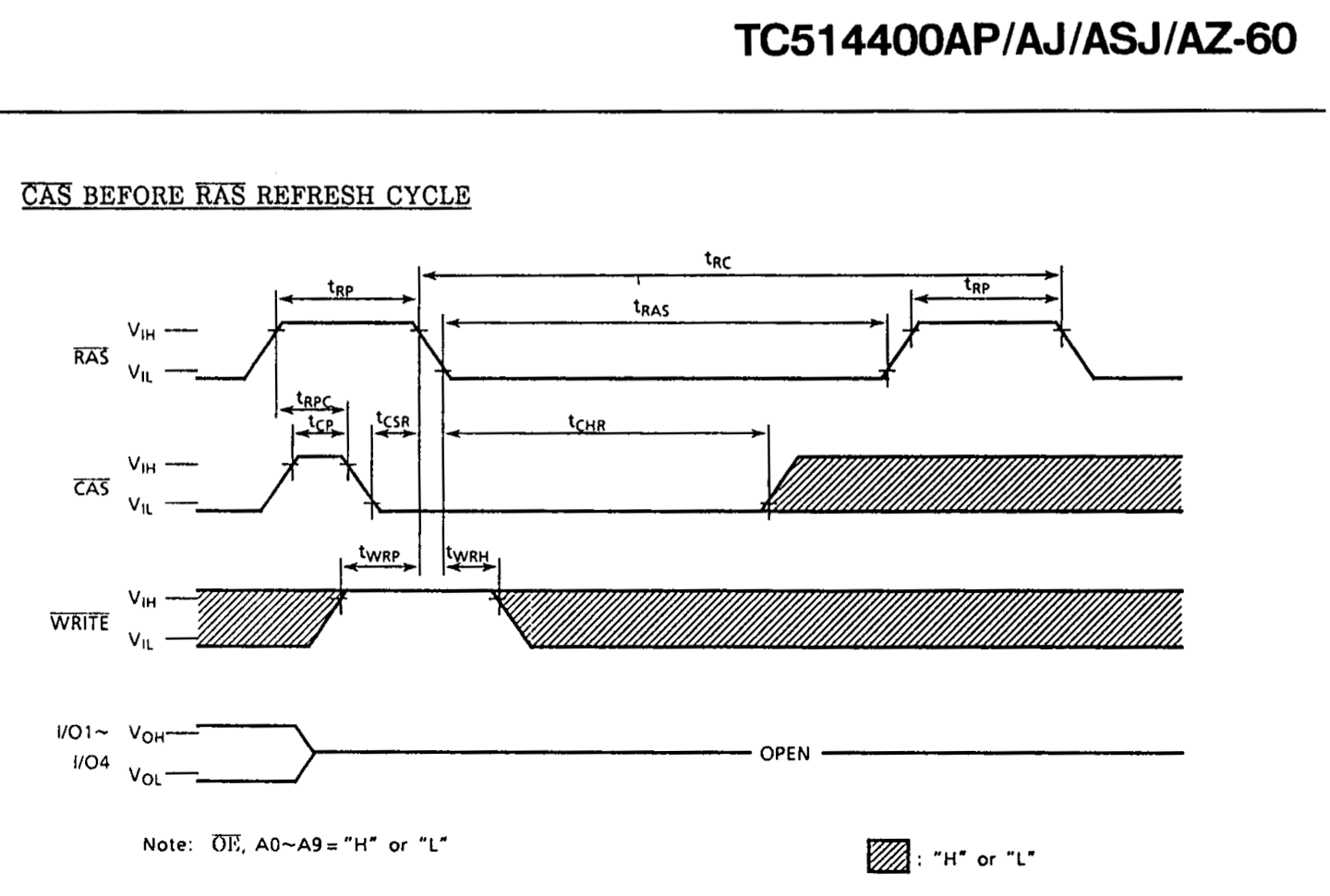

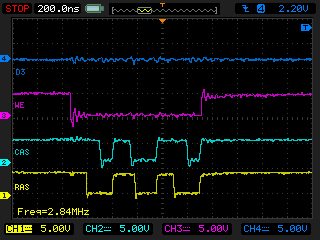

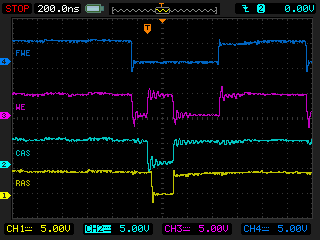

The Apple IIgs seems to perform only standard read cycles, early write cycles and CAS before RAS refresh cycles. We have not seen any fast page mode nor read-modify-write cycles.

Upon close inspection of the memory datasheets is clear that the CAS before RAS refresh cycle is different between the 1Mbit and the 4Mbit parts. In particular, the 4Mbit devices require WE to be high at the falling edge of RAS (WE is a don't care in the 1Mbit devices). Issuing a RAS before CAS refresh cycle with WE low on the 4Mbit DRAM enables the device test mode.

The IIgs follows the 1Mbit specification and the state of WE during a refresh cycle is undetermined (it is actually the state left by the transaction right before the refresh cycle). This behavior randomly enables the test mode in the memories with catastrophic results to the running programs.

The the gates U5D, U5C and the flip-flop U6A form a refresh cycle detector. The Q output of the flip-flop is high if the system is performing a RAS before CAS refresh cycle. The flip-flop will latch the value of RAS at every falling edge for CAS (this will be high only during a RAS before CAS cycle). In any case the flip-flop will be cleared on the rising edge of CAS (all cycle types end with CAS de-assertion).

Based on the output of the flip-flop, U5A and U5B force WE high if a refresh cycle is in progress.

On Sale?

How does one go about ordering one of these?

Logic Analyzer

Cool page and good writing! Love in depth articles especially when the writer knows what they are talking about and can use common speak to include those of us less versed.

Question: What Logic Analyzer are you using? Seems like a decent resolution and even PC based going by the screen caps. I'm always looking for new tools to add to the arsenal.

Thanks!

Henry

Lab Instuments

Thanks for the comment.

The screen shots are from a rigol DS1104B 4-ch oscilloscope (1GS/s 100MHz analog bandwidth). It has similar features and performance of a low end Tek scope for 1/4 of the price.

I also use the Saleae Logic which has an outstanding PC interface but I could not get a good trigger in this specific case.

Schematic Question

Hello GG.

Quick question about the schematic. Is this the final version and was it tested? A buddy of mine pointed something out and I was just curious.

Feel free to PM or email me if needed. Thanks!

Henry

Yes, the board is fully

Yes, the board is fully tested.